基础资料

PCB的信号完整性

1. 关于上升时间:

高速电路设计中,上升时间才是最关键的因素。上升时间定义为从波形的10%处上升到90%处所需要的时间(也有定义从20%到80%处)。 下降时间则为从波形的90%下降到10%处所需要的时间。正弦波的上升时间大约为周期的1/3。带宽为能够保持信号完整性的频率范围,带宽≈0.3/上升时间。

2. 关于传播时间:

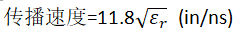

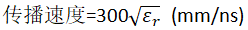

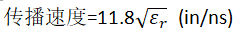

电信号在空气中以光速传播,即299792458m/s,为300mm/ns。使用英制单位为186280mile/s,约11.8in/ns。而电磁场在某种介质中的传播速度等于光速除以这种介质的介电常数的平方根:

传播时间用每单位长度所需要的时间来表示,是传播速度的倒数。空气中导线的电信号传播时间3.34ns/m,或3.34ps/mm,英制为0.085ns/in。

电路板最常用的材料是FR4,FR4是树脂和玻璃的混合物,但不是均匀的,玻璃会聚积成块,树脂则填充在周围。玻璃的相对介电常数εr约为6.0, 树脂的相对介电常数εr约为3.0,它们的混合物的平均相对介电常数εr约在4.0到4.3之间。

从信号传播角度看,位于两参考层间的走线可看作带状线,而仅在一侧有参考层的走线是微带线。FR4的相对介电常数大约为4,所以传播速度150mm/ns(英制6in/ns)。

微带线两侧介质相对介电常数不同,等效介电常数为0.457εr+0.67。实际上微带线变宽,或微带线靠近参考层时,传播时间都有变慢,不是一个常数。估算公式:

微带线的信号传播时间=Br×带状线中信号的传播时间

其中,Br=0.8566+(0.0294)lnW-0.00239H-0.0101εr,W为走线宽度,H为走线和参考层间的距离,单位mil。

使用公制时,Br=0.7486+(0.0294)lnW-0.0000607H-0.0101εr,单位mm。

因为Br<1,即信号在微带线中的传播速度永远不会比带状线中慢。

线路板设计者通过走线的长度来控制信号的时序,增加走线的长度可以增加传播时间,如果需要有一个固定的延时,可通过调整走线长度来实现,用蛇形走线。 为避免产生EMI问题,一般把调节限制在电路板内部的层上,以保证不会带来辐射问题。

3. 一些电路板分布参数计算的相关公式:

4. 关于参考层和电流回流:

参考层起控制EMI、稳定走线阻抗、控制串扰、使电源系统高频去耦的作用,减小电路板上的电感效应,特别是电源层和地层的电感更重要。

如果要把EMI辐射减少到最小,那么就让信号线尽量靠近与它构成回路的回流信号线。设计者必须知道回流信号在什么地方,因为每个信号都有一个回流信号。

电流总在闭合回路中流动,每一个信号都有一个回流信号,设计者需要考虑并控制它在电路板上的位置。回流电流总是从阻抗最小的路径上通过。 直流信号的回流电流可能位于电路板上的任何位置,交流信号的回流信号总是趋向于直接从信号的下方通过,当上升时间减小时,这种趋势会加强。 如果想把EMI减小到最小,就必须把回路面积减小到最小。

如果电路板上有足够空间,那么最好在每两个信号的引脚之间都连接一个电容到地。从交流的角度看,电源层和地层之间没有任何区别,这两个层是被旁路电容短路的。 如果有频率很高的谐波信号,并且电路板上设计了利用电源层和地层本身而形成的电容,那么回流信号就可以通过这些电容流回地层。

也有建议,在接头或者器件旁也放置旁路电容来提供回流通路,旁路电容的作用就不再是去耦,而是控制电源层上回流电流的回路面积,从而控制EMI。

高速电路中控制共模电流的方法:为每一根走线保持一个一致的、连续的参考层;如果可能,把所有的关键走线都布置成带状线;减少任何短截线, 或者减小与任何高速信号走线有关的外部走线的长度;让电源层和地层在电路板中成对出现,并保证两层间的良好电容去耦。

20H准则:高速电路板边缘辐射的减少量与其中一个层相对于另外一个层的缩进量直接相关。如果一个层相对于另一个层的边缘缩进20倍,那么电磁场的密度可减少大约70%。

桩栅栏(法拉第屏蔽):在两个地层之间放置密集的过孔,以便在电路板边缘形成屏蔽,孔间距选λ/20。对上升时间是1ns的信号,过孔间距约1in=25.4mm。

5. 短走线、长走线与阻抗匹配:

短走线:如果信号在走线上传播和返回的时间比信号的上升时间短,可以认为是短走线。

长走线:走线上传播和返回的时间比信号的上升时间长,认为是长走线,必须考虑终端阻抗匹配。

短截线长度的规则:小于1/10或1/12上升时间,对于1ns上升时间,约76~100ps,约13mm,英制0.5in。

传输线终端匹配的五种形式:

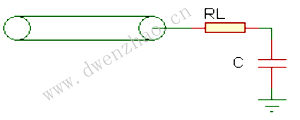

1)并联:简单,但提供了直流路径

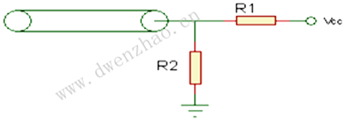

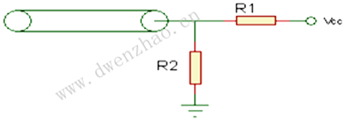

2)戴维宁:使用两个元件,Z0=R1//R2

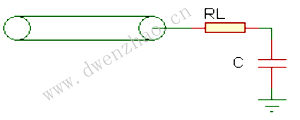

3)交流终端匹配:使用两个元件,Z0=R1//R2

4)串联:放在走线的开始,越来越常用

Rs与驱动端输出电阻的和应等于走线电阻。

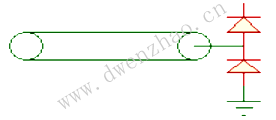

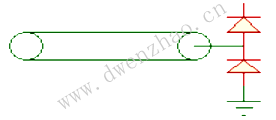

5)二极管:限制反射,可放于走线的任何位置

为了控制反射,必须控制阻抗,使走线的阻抗在整个长度上必须是恒定的。

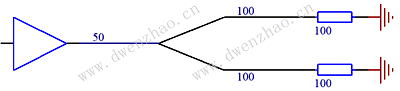

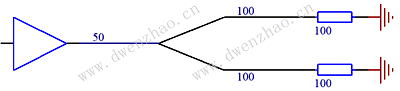

走线Y型分支:Y型分支会造成阻抗不连续

1)100Ω匹配:

设计走线阻抗为50Ω,而分支后支路阻抗为100Ω,并使用100Ω匹配。

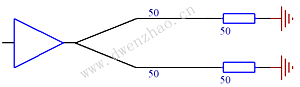

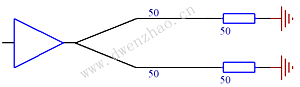

2)分支前置:

让分支的位置靠近驱动端,让阻抗不连续发生在短截线长度内。

6. 关于串扰:

两条彼此靠近的走线会产生串扰。电流沿一条走线流动(称主动线),耦合到邻近的走线(称被动线),并产生两个不同的噪声信号, 其中一个在被动线中的流动反向与主动线中的方向相同(前向串扰),另一个以相反的反向在被动线中流动(反向串扰)。

串扰有电容性耦合串扰和电感性耦合串扰。两种串扰在后向上彼此相加,而在前向上会彼此抵消,特别是在带状线情况下。 如果要减小串扰,把所有敏感走线都布置成带状线。串扰与走线到参考层间的距离的平方成反比。

反向串扰脉冲的幅度大小几乎是常数,迅速增加为恒定值,而脉冲宽度是由耦合区域表示的传播时间的2倍。在耦合区域长度大约等于驱动信号上升时间的1/2时,后向串扰脉冲的幅度达到最大值。 如果耦合区域很小,后向信号幅度也很小,随着耦合长度的增加,幅度也会增加,到关键长度时,到达最大。

前向串扰信号的幅度随着耦合区域长度的增大而不断增加,宽度不会超过产生它的驱动信号的上升时间。前向串扰在微带情况下很小,而在带状线下几乎不存在。

两走线间隔为D,走线距参考层的距离为H,则耦合程度与H2/(H2+D2)成正比,不会超过此值。减小串扰,需要为走线建立参考层,并靠近参考层,让走线间距增加,而现款影响很小。

防护带:主动走线与被动走线间布置一条接地的走线,但有时反而有负作用。

处理差分信号,注意使走线的长度相等,当走线差造成1o的相移就可能造成严重问题。频率50MHz,1o相移约333mil,500MHz时为33mil,5GHz时为3mil(在FR4板上)。 差分走线彼此靠得很近,它们的回路面积越小,EMI效果越好,且抗干扰能力越好。

7. 关于差分线:

差分阻抗:在两线间连接的一个电阻,值为两线奇模电阻之和,Zdiff=2Z0(1-k)=2(Z11-Z11)。 当每条差分线的阻抗是50Ω时,差分对的差分阻抗约80Ω。

走线距离越近,耦合越大,差分阻抗越小。可以简单地把2Z0减小20%作为差分阻抗。微带线与带状线差分阻抗公式为:

微带线差分阻抗:Zdiff=2Z0(1-0.48e-0.096s/h)

带状线差分阻抗:Zdiff=2Z0(1-0.78e-2.9s/h)

其中,Z0为单端走线阻抗,s为走线边缘到边缘的距离,h为微带线中走线参考层的高度或带状线中两个参考层间的距离。

对两根走线而言,共模阻抗约为差模阻抗的1/4。差分走线的间距必须在整个长度上保持恒定。

8. 关于去耦电容:

线路板上要求去耦的地方往往需要两个去耦电容,许多高速板上设计有平面电容。

使用旁路电容的目的是减小进行开关动作的器件中电流通路上的电感,电容放置的位置越靠近发生开关动作的器件越好,且把一些小的、反应速度更快一些的电容放置在离器件更近的位置, 放在靠近参考电压的位置。平面电容可达0.16p~0.47pF/mm2,英制为100p~300pF/in2。

所有实际的电容都带有一些电感成分,SMT电容可能会带有5~10nH的电感。

实际电容的阻抗Z=|2πfL-1/(2πfC)|=|[(2πf)2LC-1]/(2πfC)|,其中有一个自谐振频率,这时达到阻抗最小点。阻抗曲线的峰值与ESR值成反比。

电容并联并不会改变自谐振频率,但有效地增加了电容值,减小了电感及ESR的值。电容并联时,如两个电容的自谐振频率不同,它们之间会产生一个极点,称抗谐振点,阻抗为R/2+X2/2R。 如果R>>X,阻抗约为R/2,比系统的谐振点阻抗还小。如果R值在0.1~0.01之间,阻抗值可接受。

如果能让电容的值在抗谐振点有X1=-X2=ESR,那么将得到一个相对平坦的阻抗响应曲线。

9. 关于电源分区隔离和多层板参考层:

不同的电路以及同一个电路的不同级提供不同的稳压电源区域,就是为了防止一个电路产生的噪声与另一个电路中的信号相互作用、相互影响。 常常利用参考层上的缝隙把电源区域在水平上隔离开,高速设计中噪声控制是最重要的。如果电路噪声是关注的焦点,需要为每一个单独电源定义一个独立参考层。 良好的设计方法是使用独立的模拟地参考层与数字地参考层,所有的参考层通过单个点连接起来。

如果板上有多个孤立电源,彼此之间可以用0Ω电阻或磁珠在一个点连接起来。如果使用多个独立的电源,并且这些电源有自己的参考层,那么不要让这些层之间不相关的部分发生重叠。 如果对两个参考层进行了隔离,那么这两个层之间永远不要有走线穿过。

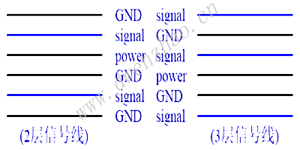

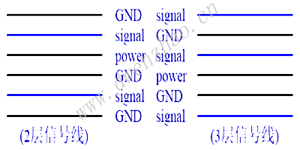

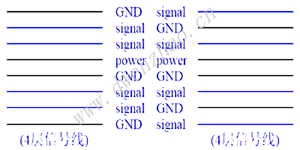

每一条高速线必须有一个连续的参考层,每一个电源应该有一对平行的电容性的电源-地参考层。高集成度的6层和8层设计法:

如果要在高速电路板中设计使用4个信号层的6层结构,就要接受一些折中。

10. 有损传输线:

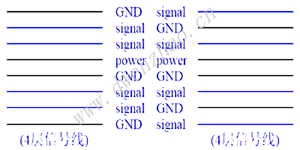

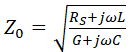

趋肤效应及介质吸收导致信号衰减,成为有损传输线。传输线损耗使特性阻抗随频率而变化:

100MHz可测到损耗效应,1GHz时会导致设计问题。眼图是观察有效传输线各种效应的有效途径。

传输线的损耗导致高频谐波的幅度被消弱,可通过高频均衡来补偿。无源高通滤波器消减低频幅度,比如简单的RC电路,可放置在传输线起始或末端,或包括在接收器件中。

有源均衡(有源预补偿):信号每次从一个状态变为另一个状态,把信号幅度变为原来的0.5倍,如果下一个脉冲时刻幅度未变化,就变为0.25倍,增大了数据流的高频成分。

11. 一些阻抗计算公式:

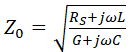

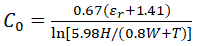

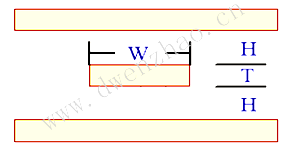

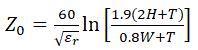

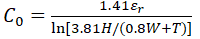

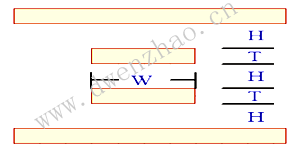

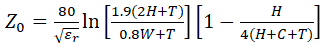

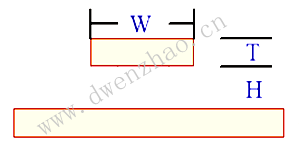

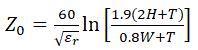

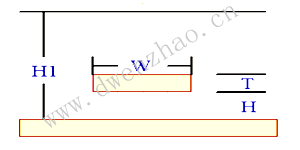

微带线:微带线宽度W,高度T,距参考层H,单位mil

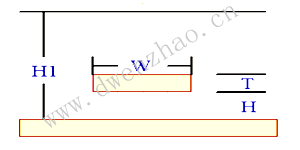

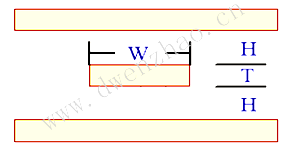

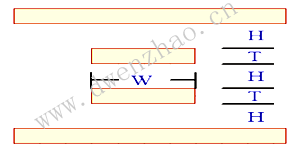

带状线:带状线宽度W,高度T,距参考层H,单位mil

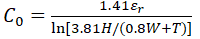

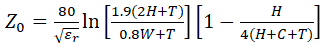

双重带状线:带状线宽度W,高度T,距参考层H,单位mil

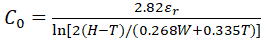

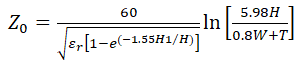

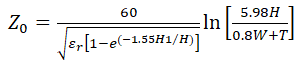

嵌入式微带线:微带线宽度W,高度T,距参考层H,介质层高度H1,单位mil

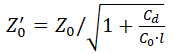

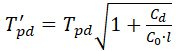

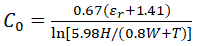

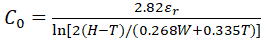

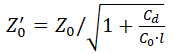

12. 容性负载的修正系数:

其中,Cd为由元件负载所增加的电容,C0为每单位长度走线的固有电容,l 为走线长度

对电阻的修正:

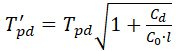

对传播时间的修正:

高速电路设计中,上升时间才是最关键的因素。上升时间定义为从波形的10%处上升到90%处所需要的时间(也有定义从20%到80%处)。 下降时间则为从波形的90%下降到10%处所需要的时间。正弦波的上升时间大约为周期的1/3。带宽为能够保持信号完整性的频率范围,带宽≈0.3/上升时间。

2. 关于传播时间:

电信号在空气中以光速传播,即299792458m/s,为300mm/ns。使用英制单位为186280mile/s,约11.8in/ns。而电磁场在某种介质中的传播速度等于光速除以这种介质的介电常数的平方根:

传播时间用每单位长度所需要的时间来表示,是传播速度的倒数。空气中导线的电信号传播时间3.34ns/m,或3.34ps/mm,英制为0.085ns/in。

电路板最常用的材料是FR4,FR4是树脂和玻璃的混合物,但不是均匀的,玻璃会聚积成块,树脂则填充在周围。玻璃的相对介电常数εr约为6.0, 树脂的相对介电常数εr约为3.0,它们的混合物的平均相对介电常数εr约在4.0到4.3之间。

从信号传播角度看,位于两参考层间的走线可看作带状线,而仅在一侧有参考层的走线是微带线。FR4的相对介电常数大约为4,所以传播速度150mm/ns(英制6in/ns)。

微带线两侧介质相对介电常数不同,等效介电常数为0.457εr+0.67。实际上微带线变宽,或微带线靠近参考层时,传播时间都有变慢,不是一个常数。估算公式:

微带线的信号传播时间=Br×带状线中信号的传播时间

其中,Br=0.8566+(0.0294)lnW-0.00239H-0.0101εr,W为走线宽度,H为走线和参考层间的距离,单位mil。

使用公制时,Br=0.7486+(0.0294)lnW-0.0000607H-0.0101εr,单位mm。

因为Br<1,即信号在微带线中的传播速度永远不会比带状线中慢。

线路板设计者通过走线的长度来控制信号的时序,增加走线的长度可以增加传播时间,如果需要有一个固定的延时,可通过调整走线长度来实现,用蛇形走线。 为避免产生EMI问题,一般把调节限制在电路板内部的层上,以保证不会带来辐射问题。

3. 一些电路板分布参数计算的相关公式:

电容量的计算公式:C(pF)=5.710εrA*(n-1)/d

其中,εr为相对介电常数,A为每块极板的面积(mm2),d为极板间的距离(mm),n为极板的个数

使用英制时,公式为:C(pF)=0.2248εrA*(n-1)/d,单位in。

空气中的导线的电感公式:L(uF)=0.128b{[ln(2b/a)]-0.75}

其中,a为导线半径(mm),b为导线长度(mm)

使用英制时,公式为:L(uF)=0.00508b{[ln(2b/a)]-0.75},单位in。

微带线的电感:L(nH)=5ln(2πh/w)

其中,h为距离参考层的高度(mil),w为走线宽度(mil)

电容上的电压电流关系:I=C*dV/dt,或 dV=(I/C)dt

电感上的电压电流关系:V=L*dI/dt,或 dI=(V/L)dt

RC电路的电容上电压:V(t)=V(1-e-t/RC),电容上的电流:I(t)=(V/R)e-t/RC

其中,时间常数RC,在RC时刻达到最终幅值的63%,3个RC时间后达到最终幅值的95%。

RL电路的电感上电流:I(t)=(V/R)(1-e-tR/L),电感上的电压:V(t)=Ve-tR/L

其中,时间常数L/R,在L/R时刻达到最终幅值的63%,3个L/R时间后达到最终幅值的95%。

容抗的表达式:XC=-1/ωC,感抗的表达式:XL=ωL

电抗的串联:XS=X1+X2,电抗的并联:XP=1/(1/X1+1/X2)

电容与电感的串联:XSLC=XL+XC=ωL-1/ωC=(ω2LC-1)/ωC

电容与电感的并联:XPLC=1/(1/XL+1/XC)=1/[-ωC+1/ωL]=ωL/(1-ω2LC)

在任何阻抗曲线上,阻抗随频率的增加而减小的部分,电路呈容性,反之呈感性。

串联谐振RLC电路Q=ωrL/R,并联谐振RLC电路Q=R/ωrL

当上升时间减小到一定程度,电路板上的寄生电容和寄生电感开始导致一些可能影响电路性能的噪声信号和瞬态信号时,就需要考虑信号完整性问题。

归纳为4个部分,EMI、反射、串扰、电源系统的稳定性。其中,εr为相对介电常数,A为每块极板的面积(mm2),d为极板间的距离(mm),n为极板的个数

使用英制时,公式为:C(pF)=0.2248εrA*(n-1)/d,单位in。

空气中的导线的电感公式:L(uF)=0.128b{[ln(2b/a)]-0.75}

其中,a为导线半径(mm),b为导线长度(mm)

使用英制时,公式为:L(uF)=0.00508b{[ln(2b/a)]-0.75},单位in。

微带线的电感:L(nH)=5ln(2πh/w)

其中,h为距离参考层的高度(mil),w为走线宽度(mil)

电容上的电压电流关系:I=C*dV/dt,或 dV=(I/C)dt

电感上的电压电流关系:V=L*dI/dt,或 dI=(V/L)dt

RC电路的电容上电压:V(t)=V(1-e-t/RC),电容上的电流:I(t)=(V/R)e-t/RC

其中,时间常数RC,在RC时刻达到最终幅值的63%,3个RC时间后达到最终幅值的95%。

RL电路的电感上电流:I(t)=(V/R)(1-e-tR/L),电感上的电压:V(t)=Ve-tR/L

其中,时间常数L/R,在L/R时刻达到最终幅值的63%,3个L/R时间后达到最终幅值的95%。

容抗的表达式:XC=-1/ωC,感抗的表达式:XL=ωL

电抗的串联:XS=X1+X2,电抗的并联:XP=1/(1/X1+1/X2)

电容与电感的串联:XSLC=XL+XC=ωL-1/ωC=(ω2LC-1)/ωC

电容与电感的并联:XPLC=1/(1/XL+1/XC)=1/[-ωC+1/ωL]=ωL/(1-ω2LC)

在任何阻抗曲线上,阻抗随频率的增加而减小的部分,电路呈容性,反之呈感性。

串联谐振RLC电路Q=ωrL/R,并联谐振RLC电路Q=R/ωrL

4. 关于参考层和电流回流:

参考层起控制EMI、稳定走线阻抗、控制串扰、使电源系统高频去耦的作用,减小电路板上的电感效应,特别是电源层和地层的电感更重要。

如果要把EMI辐射减少到最小,那么就让信号线尽量靠近与它构成回路的回流信号线。设计者必须知道回流信号在什么地方,因为每个信号都有一个回流信号。

电流总在闭合回路中流动,每一个信号都有一个回流信号,设计者需要考虑并控制它在电路板上的位置。回流电流总是从阻抗最小的路径上通过。 直流信号的回流电流可能位于电路板上的任何位置,交流信号的回流信号总是趋向于直接从信号的下方通过,当上升时间减小时,这种趋势会加强。 如果想把EMI减小到最小,就必须把回路面积减小到最小。

如果电路板上有足够空间,那么最好在每两个信号的引脚之间都连接一个电容到地。从交流的角度看,电源层和地层之间没有任何区别,这两个层是被旁路电容短路的。 如果有频率很高的谐波信号,并且电路板上设计了利用电源层和地层本身而形成的电容,那么回流信号就可以通过这些电容流回地层。

也有建议,在接头或者器件旁也放置旁路电容来提供回流通路,旁路电容的作用就不再是去耦,而是控制电源层上回流电流的回路面积,从而控制EMI。

高速电路中控制共模电流的方法:为每一根走线保持一个一致的、连续的参考层;如果可能,把所有的关键走线都布置成带状线;减少任何短截线, 或者减小与任何高速信号走线有关的外部走线的长度;让电源层和地层在电路板中成对出现,并保证两层间的良好电容去耦。

20H准则:高速电路板边缘辐射的减少量与其中一个层相对于另外一个层的缩进量直接相关。如果一个层相对于另一个层的边缘缩进20倍,那么电磁场的密度可减少大约70%。

桩栅栏(法拉第屏蔽):在两个地层之间放置密集的过孔,以便在电路板边缘形成屏蔽,孔间距选λ/20。对上升时间是1ns的信号,过孔间距约1in=25.4mm。

5. 短走线、长走线与阻抗匹配:

短走线:如果信号在走线上传播和返回的时间比信号的上升时间短,可以认为是短走线。

长走线:走线上传播和返回的时间比信号的上升时间长,认为是长走线,必须考虑终端阻抗匹配。

短截线长度的规则:小于1/10或1/12上升时间,对于1ns上升时间,约76~100ps,约13mm,英制0.5in。

传输线终端匹配的五种形式:

1)并联:简单,但提供了直流路径

2)戴维宁:使用两个元件,Z0=R1//R2

3)交流终端匹配:使用两个元件,Z0=R1//R2

4)串联:放在走线的开始,越来越常用

Rs与驱动端输出电阻的和应等于走线电阻。

5)二极管:限制反射,可放于走线的任何位置

为了控制反射,必须控制阻抗,使走线的阻抗在整个长度上必须是恒定的。

走线Y型分支:Y型分支会造成阻抗不连续

1)100Ω匹配:

设计走线阻抗为50Ω,而分支后支路阻抗为100Ω,并使用100Ω匹配。

2)分支前置:

让分支的位置靠近驱动端,让阻抗不连续发生在短截线长度内。

6. 关于串扰:

两条彼此靠近的走线会产生串扰。电流沿一条走线流动(称主动线),耦合到邻近的走线(称被动线),并产生两个不同的噪声信号, 其中一个在被动线中的流动反向与主动线中的方向相同(前向串扰),另一个以相反的反向在被动线中流动(反向串扰)。

串扰有电容性耦合串扰和电感性耦合串扰。两种串扰在后向上彼此相加,而在前向上会彼此抵消,特别是在带状线情况下。 如果要减小串扰,把所有敏感走线都布置成带状线。串扰与走线到参考层间的距离的平方成反比。

反向串扰脉冲的幅度大小几乎是常数,迅速增加为恒定值,而脉冲宽度是由耦合区域表示的传播时间的2倍。在耦合区域长度大约等于驱动信号上升时间的1/2时,后向串扰脉冲的幅度达到最大值。 如果耦合区域很小,后向信号幅度也很小,随着耦合长度的增加,幅度也会增加,到关键长度时,到达最大。

前向串扰信号的幅度随着耦合区域长度的增大而不断增加,宽度不会超过产生它的驱动信号的上升时间。前向串扰在微带情况下很小,而在带状线下几乎不存在。

两走线间隔为D,走线距参考层的距离为H,则耦合程度与H2/(H2+D2)成正比,不会超过此值。减小串扰,需要为走线建立参考层,并靠近参考层,让走线间距增加,而现款影响很小。

防护带:主动走线与被动走线间布置一条接地的走线,但有时反而有负作用。

处理差分信号,注意使走线的长度相等,当走线差造成1o的相移就可能造成严重问题。频率50MHz,1o相移约333mil,500MHz时为33mil,5GHz时为3mil(在FR4板上)。 差分走线彼此靠得很近,它们的回路面积越小,EMI效果越好,且抗干扰能力越好。

7. 关于差分线:

差分阻抗:在两线间连接的一个电阻,值为两线奇模电阻之和,Zdiff=2Z0(1-k)=2(Z11-Z11)。 当每条差分线的阻抗是50Ω时,差分对的差分阻抗约80Ω。

走线距离越近,耦合越大,差分阻抗越小。可以简单地把2Z0减小20%作为差分阻抗。微带线与带状线差分阻抗公式为:

微带线差分阻抗:Zdiff=2Z0(1-0.48e-0.096s/h)

带状线差分阻抗:Zdiff=2Z0(1-0.78e-2.9s/h)

其中,Z0为单端走线阻抗,s为走线边缘到边缘的距离,h为微带线中走线参考层的高度或带状线中两个参考层间的距离。

对两根走线而言,共模阻抗约为差模阻抗的1/4。差分走线的间距必须在整个长度上保持恒定。

8. 关于去耦电容:

线路板上要求去耦的地方往往需要两个去耦电容,许多高速板上设计有平面电容。

使用旁路电容的目的是减小进行开关动作的器件中电流通路上的电感,电容放置的位置越靠近发生开关动作的器件越好,且把一些小的、反应速度更快一些的电容放置在离器件更近的位置, 放在靠近参考电压的位置。平面电容可达0.16p~0.47pF/mm2,英制为100p~300pF/in2。

所有实际的电容都带有一些电感成分,SMT电容可能会带有5~10nH的电感。

实际电容的阻抗Z=|2πfL-1/(2πfC)|=|[(2πf)2LC-1]/(2πfC)|,其中有一个自谐振频率,这时达到阻抗最小点。阻抗曲线的峰值与ESR值成反比。

电容并联并不会改变自谐振频率,但有效地增加了电容值,减小了电感及ESR的值。电容并联时,如两个电容的自谐振频率不同,它们之间会产生一个极点,称抗谐振点,阻抗为R/2+X2/2R。 如果R>>X,阻抗约为R/2,比系统的谐振点阻抗还小。如果R值在0.1~0.01之间,阻抗值可接受。

如果能让电容的值在抗谐振点有X1=-X2=ESR,那么将得到一个相对平坦的阻抗响应曲线。

9. 关于电源分区隔离和多层板参考层:

不同的电路以及同一个电路的不同级提供不同的稳压电源区域,就是为了防止一个电路产生的噪声与另一个电路中的信号相互作用、相互影响。 常常利用参考层上的缝隙把电源区域在水平上隔离开,高速设计中噪声控制是最重要的。如果电路噪声是关注的焦点,需要为每一个单独电源定义一个独立参考层。 良好的设计方法是使用独立的模拟地参考层与数字地参考层,所有的参考层通过单个点连接起来。

如果板上有多个孤立电源,彼此之间可以用0Ω电阻或磁珠在一个点连接起来。如果使用多个独立的电源,并且这些电源有自己的参考层,那么不要让这些层之间不相关的部分发生重叠。 如果对两个参考层进行了隔离,那么这两个层之间永远不要有走线穿过。

每一条高速线必须有一个连续的参考层,每一个电源应该有一对平行的电容性的电源-地参考层。高集成度的6层和8层设计法:

如果要在高速电路板中设计使用4个信号层的6层结构,就要接受一些折中。

10. 有损传输线:

趋肤效应及介质吸收导致信号衰减,成为有损传输线。传输线损耗使特性阻抗随频率而变化:

100MHz可测到损耗效应,1GHz时会导致设计问题。眼图是观察有效传输线各种效应的有效途径。

传输线的损耗导致高频谐波的幅度被消弱,可通过高频均衡来补偿。无源高通滤波器消减低频幅度,比如简单的RC电路,可放置在传输线起始或末端,或包括在接收器件中。

有源均衡(有源预补偿):信号每次从一个状态变为另一个状态,把信号幅度变为原来的0.5倍,如果下一个脉冲时刻幅度未变化,就变为0.25倍,增大了数据流的高频成分。

11. 一些阻抗计算公式:

微带线:微带线宽度W,高度T,距参考层H,单位mil

带状线:带状线宽度W,高度T,距参考层H,单位mil

双重带状线:带状线宽度W,高度T,距参考层H,单位mil

嵌入式微带线:微带线宽度W,高度T,距参考层H,介质层高度H1,单位mil

12. 容性负载的修正系数:

其中,Cd为由元件负载所增加的电容,C0为每单位长度走线的固有电容,l 为走线长度

对电阻的修正:

对传播时间的修正: