基础资料

1. 可编程逻辑器件介绍:

可编程逻辑器件是指一切可以通过软件手段配置、更改器件内部连接结构和逻辑单元,完成既定设计功能的数字集成电路。目前,常用的可编程逻辑器件主要有简单的逻辑阵列(PAL/GAL)、复杂可编程逻辑器件(CPLD)和现场可编程逻辑阵列(FPGA)等。。

传统的数字电路设计,一种是使用标准的逻辑芯片进行搭建,如74系列、4000系列等;另一种是向厂家定制面向特定用途的专用集成电路ASIC。如果逻辑比较复杂,要使用很多片标准的逻辑芯片,占用PCB面积比较大;而使用ASIC方式则设计周期比较长,灵活性差,成本比较高。因此,就出现了PAL/GAL,这是可编程逻辑器件的早期形式,其中PAL是可编程阵列逻辑(Programmable Array Logic)的缩写,GAL是通用可编程阵列逻辑(Generic Array Logic)的缩写,它们内部结构较为简单,可编程逻辑单元多为与、或阵列,使用灵活方便且成本低,很快就替代了需要使用多片标准逻辑芯片的应用场合,目前仍在一些成本敏感的领域大量使用。

这些早期的PLD器件基本结构由输入电路、与阵列、或阵列、输出电路构成,输入电路主要由缓冲器和反相器构成,能够产生每个输入变量的原信号及反信号,这些信号被送人由多个与门构成的与阵列,形成输入信号的乘积项;与阵列的乘积项又被送人由多个或门构成的或阵列,输出乘积项之和,再由输出电路输出。器件中连接到与、或阵列的信号都要经过一个开关,用户使用时通过一定的方法改变这些开关的状态,以改变与、或阵列的连接方式,这个过程称为编程。由于逻辑函数总能表示为乘积项之和的形式,因此通过编程改变与、或阵列的连接方式。就能输出不同的乘积项之和,从而实现不同的逻辑函数。

随着工艺技术的发展和市场需要,又出现了复杂可编程逻辑器件CPLD和现场可编程逻辑阵列FPGA,单片集成规模从数百门到数百兆门以上,芯片引脚也由20~24发展到400~1000引脚,器件工作频率在50MHz以上,相当多的产品达到100MHz以上,有的公司推出嵌入各种IP核的品种,如集成了中央处理器CPU或数字处理器DSP内核的FPGA,在其上可进行软硬件协同设计,可以实现片上系统SoC(System on Chip)。

可编程逻辑器件公司主要几种在美国,比较著名的有Xilinx、Lattice、Actel、Altera、AMD、QuickLogic等,不过近些年在半导体行业大并购中,Altera已被Intel收购,而Xilinx则被AMD公司收购,Actel则并入Microchip。

2. 可编程逻辑器件的编程方法:

可编程逻辑器件有多种编程手段,常用的有熔丝型开关、反熔丝型开关、浮栅编程元件和基于SRAM的编程元件。

· 熔丝型开关:最初的可编程开关是熔丝链路,其中的与阵列及或阵列是熔丝连接的矩阵,当在乘积线上两个信号的熔丝被保留,而同一线上所有其他熔丝被烧断时,这两个输入信号被组合为线与或线或,这样留在器件内的未被烧断的熔丝模式组合产生了相应的逻辑功能。

· 反熔丝型开关:可编程低阻电路元件是一种基于反熔丝的一次可编程器件,能提供小的元件尺寸,在未编程状态通常呈现高阻(>100MΩ),当18V编程电压加上后建立双向的低电阻,编程电流小于10mA。

· 浮栅编程元件:这是目前应用最广泛的一种编程技术,包括可擦除的EPROM和电改写擦除EEPROM及闪存Flash Memory。

· SRAM:这是FPGA主要使用的编程方式。

传统的PLD器件编程,需要先将器件放置在特定的编程器上烧写,然后安装在设计好的短路板上,系统调试、测试比较麻烦,而且一旦烧写后,很难修改、升级。后来出现了在系统可编程技术ISP(In-System Programmable),可以将未编程的PLD安装到电路板中,然后根据功能要求进行编程,或者再编程。ISP技术最初由Lattice公司提出,并推出一系列ISP可编程逻辑器件,迅速得到广泛应用。ISP编程主要有3种方式,ISP、JTAG、IEEE1532,其中ISP为Lattice独有的编程方式,使用状态机实现;JTAG采用IEEE1149.1标准的边界扫描测试存取口TAP,是PLD首选的编程方法;IEEE1532是对JTAG的增强,并定义了描述编程算法和相关数据格式的软件需求,可将不同厂商的器件连接在一起,使用相同的编程软件进行编程。

3. 复杂可编程逻辑器件CPLD的基本结构:

CPLD一般都是基于乘积项的,如Lattice公司的ispMACH4000/5000系列,Altera公司的MAX7000/3000系列,Xilinx公司的XC9500、CoolRunner2系列等。内部结构主要由可编程I/O单元、基本逻辑单元、布线池/布线矩阵和其他辅助功能模块组成。基本逻辑单元是 一种称为宏单元MC(Macro Cell)的结构,本质上是由一些与、或阵列加上触发器构成,器件规模一般用MC的数目来表示,通过将若干个MC连接起来可以完成相对复杂逻辑功能。不同厂商的CPLD中MC的名称不同,Lattice公司称为通用逻辑模块GLB(Generic Logic Block),Altera公司称为逻辑阵列模块LAB(Logic Array Block),Xilinx则称为功能模块FB(Function Block),功能基本一致,结构上略有差异。

所谓乘积项实际上就是与或逻辑表达式,器件中使用与或阵列实现,每一个交叉点都是一个可编程熔丝/反熔丝,如果导通就是实现与逻辑,在与阵列后一般还有或阵列,用以完成逻辑表达式中的或关系,与或阵列配合工作,就能完成复杂的组合逻辑功能。MC中还有可编程触发器,一般也包括时钟、复位/置位功能,用以实现时序逻辑的寄存器或锁存器等功能。

CPLD中一般采用集中式布线池,本质上就是一个开关矩阵,通过结点状态可以控制不同的MC的输入与输出项之间的连接。CPLD中的布线池结构固定,所以输入管脚到输出管脚的标准延时固定,称为Pin to Pin延时,用Tpd表示,反映了器件可以实现的最高频率。CPLD一般还集成了JTAG模块,还包括全局时钟、全局使能、全局复位/置位单元等。

4. 现场可编程逻辑阵列FPGA:

FPGA内部结构分为可编程输入/输出单元、基本可编程逻辑单元、嵌入式RAM、布线资源、底层嵌入式功能单元、内嵌专用硬核等。FPGA一般是基于SRAM工艺的,其基本可编程单元一般是由查找表LUT(Look Up Table)和寄存器Register组成,LUT用于完成组合逻辑功能。FPGA有内部寄存器,可以配置为同步/异步复位或置位的时序使能触发器,也可以配置为锁存器Latch,FPGA利用内部寄存器实现同步时序逻辑功能。

目前,大部分FPGA都在内部集成了DLL或PLL硬件电路,用以完成时钟的高精度、低抖动的倍频、分频、占空比调整、移相等功能。高端FPGA则将DSP或CPU等软处理核集成在内,成为系统级设计平台,比较适合实现FIR滤波器、编码/解码、快速傅里叶变换FFT等应用。

5. Lattice公司的ispLSI CPLD器件:

Lattice公司在1992年推出了ISP技术的可编程逻辑器件,即在系统可编程,可以在用户板上编程或再编程,系统功能的更新也可以在应用现场直接在系统进行,对产品开发和升级带来便利。近些年推出的CPLD产品几乎都采用的ISP技术,原先的脱机编程方法被淘汰。Lattice公司的相关器件分为7个系列,另有原AMD公司的MACH4系列。

1) ispLSI 1000:

这是基本系列,单片集成度2000~8000门,适用于高速编码、总线管理、DMA控制等。其中E系列增加了两个全局输出许可控制信号和输出上升速率可编程控制,EA系列支持IEEE 1149.1边界扫描。

| 性能参数\型号 | 1016/1016E/A | 1024/1026E/A | 1032/1032E/A | 1048/1048E/A |

|---|---|---|---|---|

| 集成度(PLD门) | 2000 | 4000 | 6000 | 8000 |

| 最高工作频率/MHz | 125 | 125 | 125 | 90 |

| 传输延时/ns | 7.6 | 7.6 | 7.5 | 10 |

| 通用逻辑模块GLB数 | 16 | 24 | 32 | 48 |

| 触发器数 | 96 | 144 | 192 | 288 |

| 输入+I/O数 | 4+32 | 6+48 | 8+64 | 110 |

| 封装 | 44PLCC/TQFP | 68PLCC/100TQFP | 84PLCC/100TQFP | 128PQFP/133CPGA |

2) ispLSI 2000:

这高速系列,I/O端口较多,单片集成度1000~8000门,适用于高速计数、定时等场合,并可用于高速RISC/CISC微处理器接口,因系列比较齐全,应用广泛,其中2000E和2000/A支持5V,2000VE支持3.3V,2000VL支持2.5V。

| 性能参数\型号 | 2032A/E/VE/VL | 2064A/E/VE/VL | 2096A/E/VE/VL | 2128A/E/VE/VL | 2192VE/VL |

|---|---|---|---|---|---|

| 集成度(PLD门) | 1000 | 2000 | 4000 | 6000 | 8000 |

| 最高工作频率/MHz | 180/255/300/180 | 125/200/280/165 | 125/200/280/165 | 100/180/250/150 | 225/150 |

| 传输延时/ns | 5.0/3.5/3.0/5.0 | 7.5/4.5/3.5/5.5 | 7.5/4.5/3.5/5.5 | 10/5.0/4.0/6.0 | 4.5/6.0 |

| 宏单元数 | 32 | 64 | 96 | 128 | 192 |

| 寄存器数 | 32 | 64 | 96 | 128 | 192 |

| 输入+I/O数 | 35 | 38/70 | 104 | 138/74 | 107/110 |

| 封装 | 44PLCC/TQFP | 44PLCC/100TQFP/100BGA | 128TQFP | 100TQFP/100BGA | 128TQFP/144BGA |

3) 其他系列:

· ispLSI 3000:这是高密度系列,单片集成度7000~14000门,能容纳较大的逻辑系统,适用于数字信号处理、图形处理、数据加密/解密/压缩等

· ispLSI 6000:这是有片上RAM和FIFO的产品,单片集成度25000门

· ispLSI 5000:这是超宽系列,适用于32位和64位宽逻辑应用

· ispLSI 8000:这是超大系列,单片集成度达6万门,并支持片内三态总线,适用于高性能的单片系统级的实现,如高性能的接口控制、算术运算协处理器等

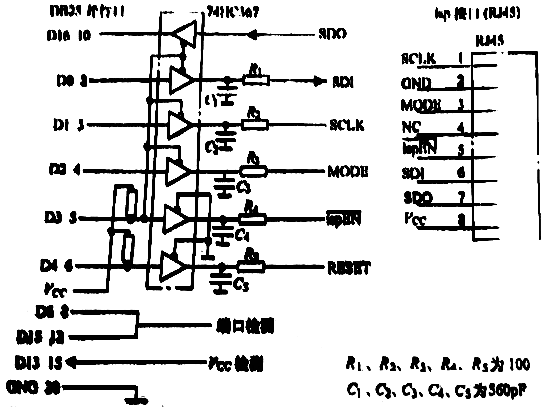

4) 编程接口:

Lattice公司提供JTAG和ISP编程接口,大部分产品支持JTAG。JTAG是符合IEEE 1149.1测试标准的接口,有4条控制线:

· TMS:测试模式选择,低电平时器件处于测试模式

· TCK:测试时钟

· TDI:测试数据串行输入,在TCK上升沿时数据装入寄存器

· TDO:串行数据输出,在TCK下降沿改变状态,并仅在数据移位输出时有效,其余时间为高阻

Lattice公司的早期产品不符合IEEE 1149.1-1990,但其特性仍然符合JTAG接口要求,称为ISP接口,包括5条控制线:ispEN-、MODE、SCLK、SDI、SDO

其DB25及RJ45电缆连接图为: